Design import Analysis of Digital IC Backend Implementation Flow

I have just applied a blog named ic backend implementation.In the later many years, I will share my working experience on digital ic backend design . So welcome all of you to come to my blog,thank you. Today i will introduce all detail things of initial design in ic backend implementation or APR (Auto Placed & Route) flow.

Front-end file

- Gate Level Netlist

Digital front-end engineers or R2N colleagues will release a gate-level netlist when releasing things to the back-end engineers. This netlist is a gate-level netlist generated by logical synthesis based on RTL or gtech files. This netlist contains all the sub-modules of the current block. The hierarchy is called. Finally, there is a top-level design. This top-level name is what we call the design module name. In addition, it also pointed out which input ports and output ports of the block, and those cells in the standard cell library are used in the block.

- Timing Constraint

The timing constraint file has the same effect throughout the digital IC design process. It is a guide tool that optimizes logic and timing based on a specific target. A timing constraint file needs to contain the following parts:

crete_clock –name CLK -period 10 [get_ports clk]

set_clock_uncertainty -setup 0.1 [all_clocks]

set_max_transition –max 0.2 [current_design]

set_max_transition 0.1 -clock CLK

set load 50 [all_outputs]

set_max_fanout 40 [current_design]

set_dont_touch $cells

set_input_delay –clock -max [get_ports **]

set_input_delay –clock -min [get_ports **]

set_output_delay -clock -max [get_ports **]

set_output_delay -clock –min [get_ports **]

set_multicycle_path 3 -setup -end -from ***

set_multicycle_path 2 -hold -end -from ***

set_false_path -from ** -to **

set_clock_group –async -name ic-backend -group {A B} -group {C D}

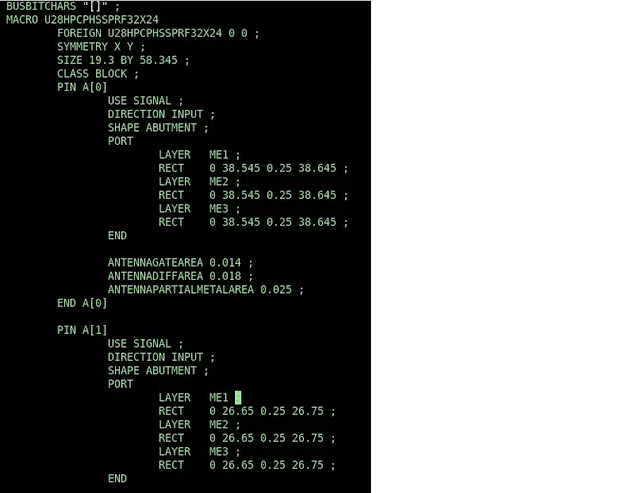

- Memory lef file

Front-end engineers will generate corresponding files when the compiler corresponds to memory, such as LEF, DB and GDS files. This Memory lef is provided to the back-end engineers for the milkyway.

- Information statistics of pre-layout after Design Compiler

In the regular flow, in the release gate level netlist, you need to attach the logically integrated pure logical area, memory area, io port number, IO PAD number and ip and other related information. Because this information can help digital back-end engineers to complete the module's area estimation more quickly, especially when a stage RTL change is relatively large.

- Prime Time QA report

Before releasing the netlist, senior engineers will definitely perform QA on the design in Prime time, check whether the current design timing is acceptable, and check whether the memory has a min period or not.

Files provided by Foundary

- Process library lef file, timing model db file

The Lef file and the db file are mainly used to make the Milkyway library and the NDM library.

- Process tech file

Techfile files are generally provided by Foundary, and of course by third-party Vendor. For example, ARM may provide their own standard cell and memory library for customers.

This tech file file is mainly used for the APR (Auto Place And Route) tool, and the guide tool is used for winding. This file will give information about the min width, min space and related definitions of via for each layer of Metal.

Here is a question: Since this tech file specifies the metal layer, the rule information between vias, can you use the DRC result after winding in ICC/ICC2 as the result of signoff drc (ie, do not run calibre DRC)?

- Antenna rule file

Foundary generally provides antenna rule files, given in clf format. At this point, you need to change to the tcl format of ICC or ICC2. The following figure shows the antenna tcl file for ICC2, which you can compare with the clf file. Regarding the definition of the antenna layer, I hope that everyone can figure out, and sometimes it may need to be changed. I love the IC community's Xiaobian mentioned in this article in the previous article.

- Tluplus file and layer map file

This file provides RC related information, mainly for the tool to estimate the delay information.

Things that digital back-end engineers need to prepare

- Milkyway and NDM generation

Why use Milkyway and NDM? Milkyway is for ICC and NDM is for ICC2. To put it simply, MIlkyway is an abstraction for GDS, because it has a small file size and enough information for the PR tool. Some people may say that you use GDS directly. Do you want to play with dead tools? The production of Milkyway actually contains three types of information, Blockage, Pin, Via, which is commonly known as BPV. In short, it is Milkyway that tells the tool how big this ip is, what signal pin, power ground pin, where there are blocks, where to punch.

About the production scripts of Milkyway and NDM, Xiaobian has already shared the knowledge planet before, and friends who need it can go to view.

- Check timing constraint file

Before reading in the netlist, you need to check the timing constraint file constraint provided by the front end to check whether the clock cycle meets the spec? Check if the timing constraint is missing. Check if there is a constraint on the ideal network?

- Read in netlist and DC constraint

After completing the above preparations, you can read the netlist and DC constraint of the design. There are often people who ask questions about reading netlists. Here are a few simple reasons for common mistakes:

- Reference library missing

- Netlist contains cells that are not mapped to standard cell libraries, such as cells with GTECH.

- TOP module name designation error

- The sub-module's milkyway and db files are inconsistent (mainly the two ports are inconsistent)

After successfully reading the design's netlist and constraint, the design is completed, and the first step of initial design is completed.

Ok, today's sharing is here. The next issue will be about sharing content on the floorplan in the digital IC backend implementation.

Attachment:

The whole reference scripts of initial design as belowed.

set search_path "<.db_file_paths>"

set link_library "* std_lib1.db std_lib2.db"

create_mw_lib my_design_lib

-technology <milkyway_techfile>

-mw_reference_library "<milkyway_lib1 milkyway_lib2>

set_tlu_plus_files \

-max_tluplus $DVAR(tlup_file,RC_MAX) \

-min_tluplus $DVAR(tlup_file,RC_MIN) \

-tech2itf_map $DVAR(layer_map_mdb_2_itf)

check_tlu_plus_files

read_verilog $DVAR(design,verilog) -top $DVAR(design,top_name)

current_design $DVAR(design,top_name)

#uniquify_fp_mw_cel

link -f

link_physical_library

###source sdc

read_sdc -e $DVAR(design,sdc)

save_mw_cel -as init

Comments

Post a Comment