Design import Analysis of Digital IC Backend Implementation Flow

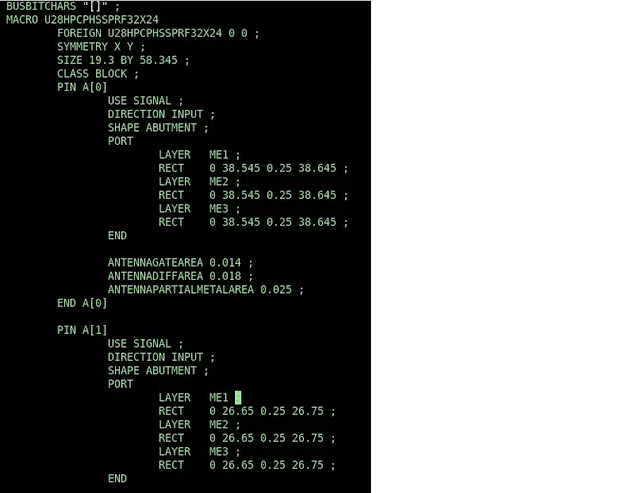

I have just applied a blog named ic backend implementation.In the later many years, I will share my working experience on digital ic backend design . So welcome all of you to come to my blog,thank you. Today i will introduce all detail things of initial design in ic backend implementation or APR (Auto Placed & Route) flow. Front-end file Gate Level Netlist Digital front-end engineers or R2N colleagues will release a gate-level netlist when releasing things to the back-end engineers. This netlist is a gate-level netlist generated by logical synthesis based on RTL or gtech files. This netlist contains all the sub-modules of the current block. The hierarchy is called. Finally, there is a top-level design. This top-level name is what we call the design module name. In addition, it also pointed out which input ports and output ports of the block, and those cells in the standard cell library are used in the block. Timing Constraint The timing constraint file has the s